### Virtual Machine Showdown: Stack versus Registers

by

Yunhe Shi, BSc. MSc.

#### Dissertation

Presented to the

University of Dublin, Trinity College

in fulfillment

of the requirements

for the Degree of

### Doctor of Philosophy

### University of Dublin, Trinity College

November 2007

## Declaration

I, the undersigned, declare that this work has not previously been submitted as an exercise for a degree at this, or any other University, and that unless otherwise stated, is my own work.

Yunhe Shi

September 1, 2007

## Permission to Lend and/or Copy

I, the undersigned, agree that Trinity College Library may lend or copy this thesis upon request.

Yunhe Shi

September 1, 2007

## Acknowledgments

I would like to express my sincere gratitude to my supervisor, Dr David Gregg. His encouragement, patience, understanding, guidance, and financial support ensured the completion of this dissertation. Since English is not my native language, he has spent a considerable time and effort to correct countless grammatical and spelling errors in my papers and thesis . Without him, it would not have been possible for me to finish my PhD.

I would like to thank Griffith College Dublin for half of the PhD fee sponsorship. I would like to thank the staff of the computing faculty at Griffith College Dublin for their kind supports. Particular gratitude to Eamonn Nolan, Tony Mullins, Kevin Hely, and Waseem Akhtar.

I would also like to thank the members of the Computer Architecture Group who have been great company and of great assistance through the years. Particular thanks to Kevin Casey and Andrew Beatty from the group, with whom I have worked on many issues relating to the Java Virtual Machine. Thanks also go to Nicholas Nash and Paul Biggar, who spent their precious time proof-reading the draft of this dissertation.

Special thanks are also due to M. A. Ertl of the Technical University, Vienna, for his unselfish assistance and ready availability to offer advice throughout the duration of this project.

Finally, my greatest appreciation is reserved for my parents for their support during my study for the PhD.

YUNHE SHI

University of Dublin, Trinity College November 2007

### Virtual Machine Showdown: Stack versus Registers

Publication No.

Yunhe Shi, Ph.D. University of Dublin, Trinity College, 2007

Supervisor: Dr. David Gregg

Virtual machines (VMs) enable the distribution of programs in an architectureneutral format, which can easily be interpreted or compiled. The most popular VMs, such as the Java virtual machine (JVM), use a virtual stack architecture, rather than the register architecture that are most popular in real processors. A long-running question in the design of VMs is whether a stack architecture or register architecture can be implemented more efficiently with an interpreter. On the one hand, stack architectures allow smaller VM code so less code must be fetched per VM instruction executed. On the other hand, stack machines require more VM instructions for a given computation, each of which requires an expensive (usually unpredictable) indirect branch for VM instruction dispatch. This dissertation extends existing work on comparing virtual stack and virtual register architectures in three ways. Firstly, we generate very high quality register code. The result is that our register code has 46% fewer executed VM instructions compared to optimized JVM stack code, with the bytecode size of the register machine being only 26% larger than that of the corresponding stack code. Secondly we present a fully functional virtual-register implementation of the Java virtual machine (JVM), which supports Intel, AMD64, PowerPC and Alpha processors. This register VM supports inline-threaded, direct-threaded, token-threaded, and switch dispatch. Thirdly, we present experimental results on a range of additional optimizations such as register allocation and elimination of redundant heap loads. On the AMD64 architecture the register machine using switch dispatch achieves an average speedup of 1.48 over the corresponding stack machine. Even using the more efficient inline-threaded dispatch, the register VM achieves a speedup of 1.15 over the equivalent stack-based VM.

The performance of VM interpreters is much affected by indirect branches and during the course of the work on VM interpreters we identified a strong interaction between the indirect branch predictor and the trace cache. The dissertation investigates the related phenomenon, and shows that the interaction between the two components results in significant improvements in indirect branch prediction. This is particularly true for codes with many indirect branches, such as VM interpreters.

# Contents

| Acknow  | wledgn              | nents                                               | iv   |

|---------|---------------------|-----------------------------------------------------|------|

| Abstra  | $\operatorname{ct}$ |                                                     | vi   |

| List of | Tables              | 3                                                   | xii  |

| List of | Figure              | 25                                                  | xiii |

| Chapte  | er 1 II             | ntroduction                                         | 1    |

| 1.1     | Motiva              | ation                                               | 1    |

| 1.2     | Our T               | hesis                                               | 2    |

| 1.3     | Contri              | butions                                             | 2    |

| 1.4     | Collab              | orations                                            | 4    |

| 1.5     | Overvi              | iew                                                 | 5    |

| Chapte  | er 2 B              | Background                                          | 7    |

| 2.1     | Introd              | uction                                              | 7    |

| 2.2     | Virtua              | l Machines                                          | 7    |

|         | 2.2.1               | High-Level Language VMs                             | 7    |

|         | 2.2.2               | The Pascal P-Code Virtual Machine                   | 9    |

| 2.3     | The Ja              | ava Virtual Machine                                 | 9    |

|         | 2.3.1               | The Internal Architecture of a Java Virtual Machine | 10   |

|         | 2.3.2               | Execution Engine                                    | 12   |

|         | 2.3.3               | Java Bytecode Instruction Set                       | 13   |

| 2.4     | Moder               | n Processor Architecture                            |      |

|         | 2.4.1               | Cache Memory                                        | 14   |

|        | 2.4.2                        | Pipelining                                     | 16 |  |  |  |  |  |

|--------|------------------------------|------------------------------------------------|----|--|--|--|--|--|

|        | 2.4.3                        | Branch Prediction                              | 17 |  |  |  |  |  |

| 2.5    | Conclu                       | usion                                          | 19 |  |  |  |  |  |

| Chapte | er 3 L                       | Literature Survey                              | 20 |  |  |  |  |  |

| 3.1    | Introd                       | luction                                        | 20 |  |  |  |  |  |

| 3.2    | Virtual Machine Interpreters |                                                |    |  |  |  |  |  |

| 3.3    | Dispat                       | tch Cost Reduction Techniques                  | 23 |  |  |  |  |  |

|        | 3.3.1                        | switch Dispatch                                | 23 |  |  |  |  |  |

|        | 3.3.2                        | Token-Threaded Dispatch                        | 26 |  |  |  |  |  |

|        | 3.3.3                        | Direct-Threaded Dispatch                       | 27 |  |  |  |  |  |

|        | 3.3.4                        | Indirect-Threaded Dispatch                     | 27 |  |  |  |  |  |

|        | 3.3.5                        | Static Superinstructions                       | 29 |  |  |  |  |  |

|        | 3.3.6                        | Inline-Threaded Dispatch                       | 29 |  |  |  |  |  |

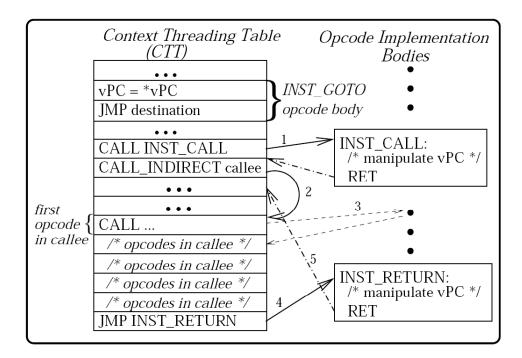

|        | 3.3.7                        | Context-Threaded Dispatch                      | 30 |  |  |  |  |  |

|        | 3.3.8                        | Vmgen Interpreter Generator                    | 32 |  |  |  |  |  |

|        | 3.3.9                        | Summary                                        | 32 |  |  |  |  |  |

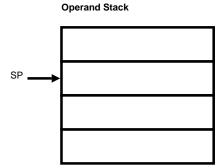

| 3.4    | Interp                       | reter Stack Caching                            | 32 |  |  |  |  |  |

| 3.5    | Regist                       | er Machines                                    | 36 |  |  |  |  |  |

|        | 3.5.1                        | Stack vs. Register Instruction Sets            | 36 |  |  |  |  |  |

|        | 3.5.2                        | Register-Based Virtual Machines                | 38 |  |  |  |  |  |

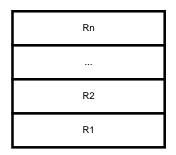

|        | 3.5.3                        | Virtual Register Organization                  | 40 |  |  |  |  |  |

|        | 3.5.4                        | Java Virtual Machine Related Research          | 41 |  |  |  |  |  |

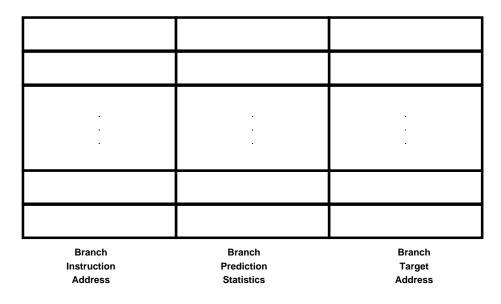

| 3.6    | Indire                       | ct Branch Prediction                           | 41 |  |  |  |  |  |

|        | 3.6.1                        | BTB with 2-bit Counters                        | 43 |  |  |  |  |  |

|        | 3.6.2                        | 2-Level Prediction of Indirect Branches        | 43 |  |  |  |  |  |

| 3.7    |                              | Cache                                          | 45 |  |  |  |  |  |

| 3.8    | Conclu                       | usion                                          | 50 |  |  |  |  |  |

| Chapte | er 4 1                       | The Trace Cache and Indirect Branch Prediction | 51 |  |  |  |  |  |

| 4.1    | Introd                       | luction                                        | 51 |  |  |  |  |  |

| 4.2    | Backg                        | round                                          | 53 |  |  |  |  |  |

|        | 4.2.1                        | Trace Cache                                    | 53 |  |  |  |  |  |

|       | 4.2.2                    | Indirect Branch Prediction                            | 55  |  |  |  |  |

|-------|--------------------------|-------------------------------------------------------|-----|--|--|--|--|

| 4.3   | Indire                   | ct Branch Prediction using Trace Cache                | 55  |  |  |  |  |

| 4.4   | 4 Experimental Framework |                                                       |     |  |  |  |  |

| 4.5   | Initial                  | Prediction Accuracies                                 | 61  |  |  |  |  |

|       | 4.5.1                    | BTB versus Trace Cache with Non-update Policy         | 61  |  |  |  |  |

|       | 4.5.2                    | Trace Cache with Update Policy                        | 63  |  |  |  |  |

| 4.6   | Predic                   | tion Accuracies of Various Trace Cache Configurations | 66  |  |  |  |  |

|       | 4.6.1                    | Trace Packing                                         | 67  |  |  |  |  |

|       | 4.6.2                    | 2-bit Saturating Update Counter                       | 68  |  |  |  |  |

|       | 4.6.3                    | Trace Cache Associativity                             | 70  |  |  |  |  |

|       | 4.6.4                    | Trace Cache Size Variance                             | 72  |  |  |  |  |

|       | 4.6.5                    | Trace Cache Line Size Variance                        | 72  |  |  |  |  |

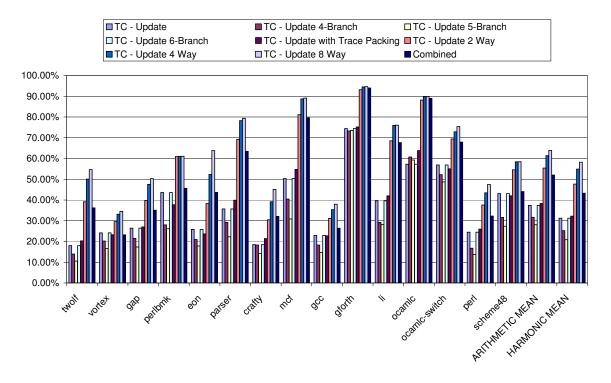

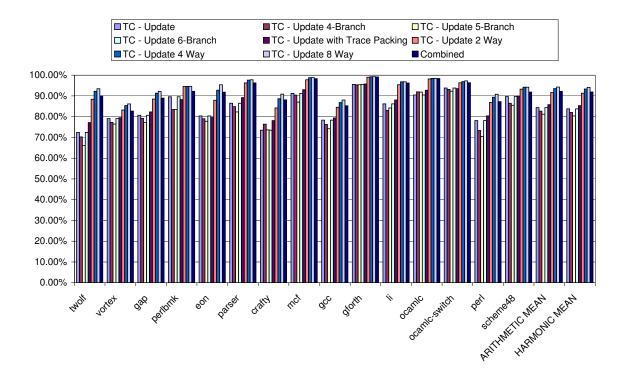

|       | 4.6.6                    | Combining Various Configurations                      | 76  |  |  |  |  |

| 4.7   | Other                    | Trace Cache Models                                    | 78  |  |  |  |  |

|       | 4.7.1                    | Real World Trace Cache                                | 78  |  |  |  |  |

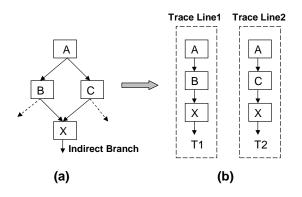

|       | 4.7.2                    | Trace Cache Context Study                             | 80  |  |  |  |  |

|       | 4.7.3                    | Other Predictors                                      | 82  |  |  |  |  |

| 4.8   | Relate                   | ed Work                                               | 83  |  |  |  |  |

| 4.9   | Conclu                   | usion                                                 | 84  |  |  |  |  |

| Chapt | or 5 S                   | Stack Architecture versus Register Architecture       | 85  |  |  |  |  |

| 5.1   |                          |                                                       | 85  |  |  |  |  |

| 5.2   |                          |                                                       | 88  |  |  |  |  |

| 0.2   | 5.2.1                    |                                                       | 89  |  |  |  |  |

|       | 5.2.1                    |                                                       | 90  |  |  |  |  |

|       |                          |                                                       | 91  |  |  |  |  |

| 5.3   |                          |                                                       | 91  |  |  |  |  |

| 0.0   | 5.3.1                    | -                                                     | 92  |  |  |  |  |

|       | 5.3.2                    |                                                       | 94  |  |  |  |  |

|       | 5.3.3                    |                                                       | 94  |  |  |  |  |

|       | 5.3.4                    |                                                       | 97  |  |  |  |  |

| 5.4   |                          |                                                       | 98  |  |  |  |  |

| J. 1  |                          |                                                       | ~ ~ |  |  |  |  |

| Chapte  | er 6 Experimental Evaluation of Stack/Register Virtual Machines101 |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------|--|--|--|--|--|--|

| 6.1     | Introduction                                                       |  |  |  |  |  |  |

| 6.2     | Setup                                                              |  |  |  |  |  |  |

| 6.3     | Static Instruction Analysis of Register Code                       |  |  |  |  |  |  |

| 6.4     | Stack Frame Space                                                  |  |  |  |  |  |  |

| 6.5     | Dynamic Instruction Analysis of Register Code                      |  |  |  |  |  |  |

| 6.6     | Code Size                                                          |  |  |  |  |  |  |

| 6.7     | CPU Loads and Stores                                               |  |  |  |  |  |  |

| 6.8     | Timing Results                                                     |  |  |  |  |  |  |

| 6.9     | Performance Counter Results                                        |  |  |  |  |  |  |

| 6.10    | Dispatch Comparison                                                |  |  |  |  |  |  |

| 6.11    | Discussion                                                         |  |  |  |  |  |  |

| 6.12    | More Optimizations                                                 |  |  |  |  |  |  |

|         | 6.12.1 Redundant Heap Load Elimination                             |  |  |  |  |  |  |

|         | 6.12.2 Stack Caching for Stack VM                                  |  |  |  |  |  |  |

|         | 6.12.3 Static Superinstructions                                    |  |  |  |  |  |  |

|         | 6.12.4 Two-Address Instructions                                    |  |  |  |  |  |  |

| 6.13    | Applicability of Results to Related Questions                      |  |  |  |  |  |  |

| 6.14    | Conclusions                                                        |  |  |  |  |  |  |

| Chapte  | er 7 Final Thoughts 126                                            |  |  |  |  |  |  |

| 7.1     | Experimentation and Systems Research                               |  |  |  |  |  |  |

| 7.2     | Stack versus Register Virtual Machines                             |  |  |  |  |  |  |

| 7.3     | 3 Future Work                                                      |  |  |  |  |  |  |

|         | 7.3.1 Compiling Source Directly Into Register-Based Code 128       |  |  |  |  |  |  |

|         | 7.3.2 Object Field Access Optimization                             |  |  |  |  |  |  |

|         | 7.3.3 Register Instruction Architecture                            |  |  |  |  |  |  |

|         | 7.3.4 Bytecode Verification                                        |  |  |  |  |  |  |

| 7.4     | Conclusion                                                         |  |  |  |  |  |  |

| Bibliog | raphy 131                                                          |  |  |  |  |  |  |

# List of Tables

| 4.1 | Benchmark statistics                                                       | 60  |

|-----|----------------------------------------------------------------------------|-----|

| 4.2 | Baseline model                                                             | 60  |

| 4.3 | Base trace cache model                                                     | 61  |

| 4.4 | Pentium 4 indirect branch prediction results on simple benchmark $\ . \ .$ | 79  |

|     |                                                                            |     |

| 6.1 | Hardware and software configuration                                        | 102 |

| 6.2 | The frame size comparison of register and stack-based VMs                  | 104 |

# List of Figures

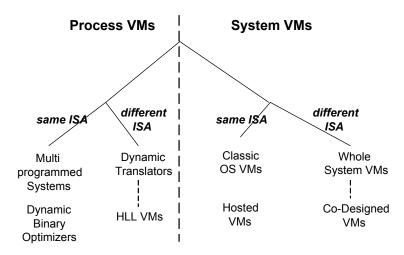

| 2.1                                     | Virtual machine taxonomy                                  | 8                                                                      |

|-----------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------|

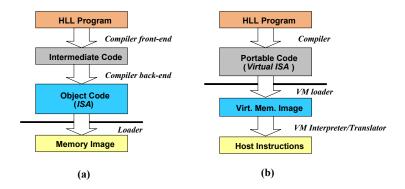

| 2.2                                     | High-level-language environments                          | 9                                                                      |

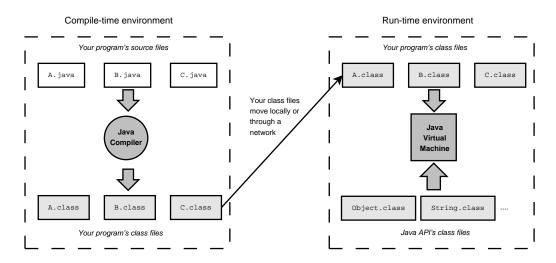

| 2.3                                     | The Java programming environment.                         | 10                                                                     |

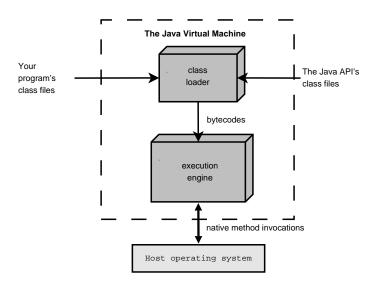

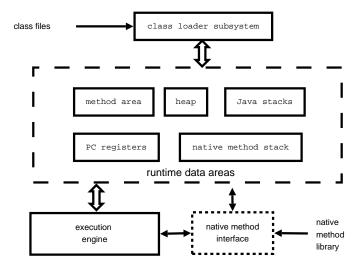

| 2.4                                     | The Java virtual machine implementation.                  | 11                                                                     |

| 2.5                                     | The internal architecture of the Java Virtual Machine.    | 11                                                                     |

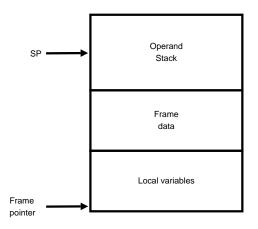

| 2.6                                     | Java frame data structure on the Java stacks.             | 12                                                                     |

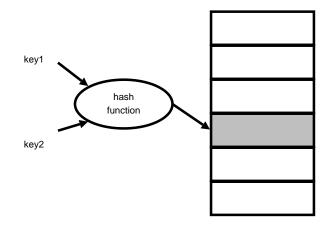

| 2.7                                     | Direct-mapped cache                                       | 15                                                                     |

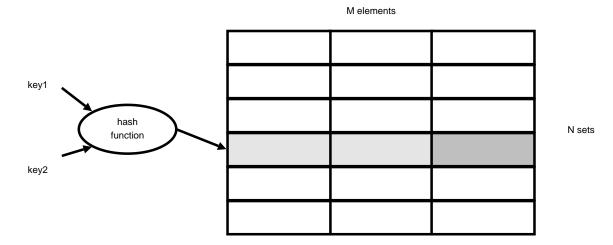

| 2.8                                     | Set-associative cache                                     | 15                                                                     |

| 2.9                                     | Classic processor pipeline                                | 16                                                                     |

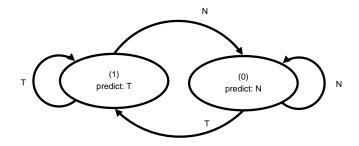

| 2.10                                    | Dynamic 1-Bit Predictor                                   | 17                                                                     |

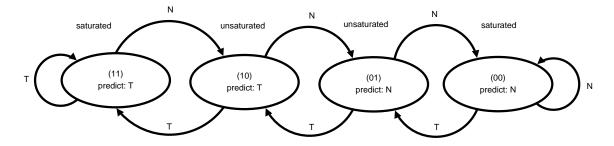

| 2.11                                    | Dynamic 2-Bit Predictor                                   | 18                                                                     |

| 2.12                                    | Two-level adaptive branch predictor.                      | 18                                                                     |

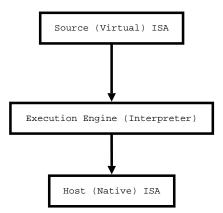

| 3.1                                     | Source and target ISA for an interpreter                  | 20                                                                     |

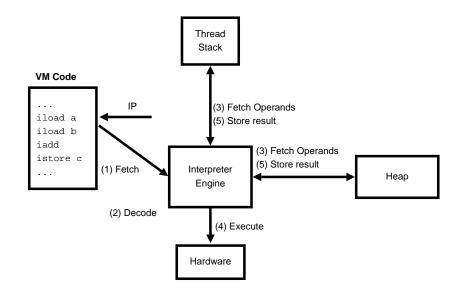

| 3.2                                     | The execution cycle of a VM instruction by an interpreter | 22                                                                     |

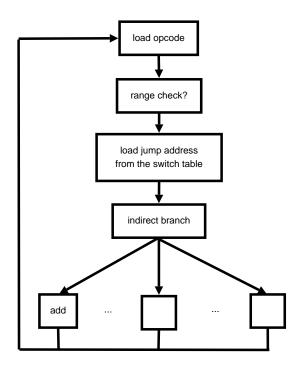

| 3.3                                     | switch interpreter dispatch                               | 23                                                                     |

| 3.4                                     |                                                           | 20                                                                     |

| 0.4                                     | switch dispatch in MIPS assembly                          | 23<br>24                                                               |

| 3.4<br>3.5                              |                                                           |                                                                        |

|                                         | switch dispatch in MIPS assembly                          | 24                                                                     |

| 3.5                                     | <pre>switch dispatch in MIPS assembly</pre>               | 24<br>25                                                               |

| $3.5 \\ 3.6$                            | <pre>switch dispatch in MIPS assembly</pre>               | 24<br>25<br>26                                                         |

| 3.5<br>3.6<br>3.7                       | switch dispatch in MIPS assembly                          | 24<br>25<br>26<br>28                                                   |

| 3.5<br>3.6<br>3.7<br>3.8                | switch dispatch in MIPS assembly                          | 24<br>25<br>26<br>28<br>28                                             |

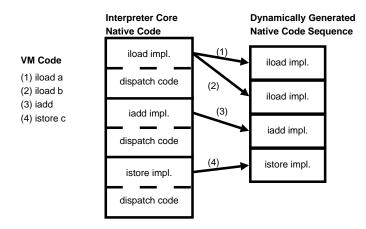

| 3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10 | switch dispatch in MIPS assembly                          | <ul> <li>24</li> <li>25</li> <li>26</li> <li>28</li> <li>30</li> </ul> |

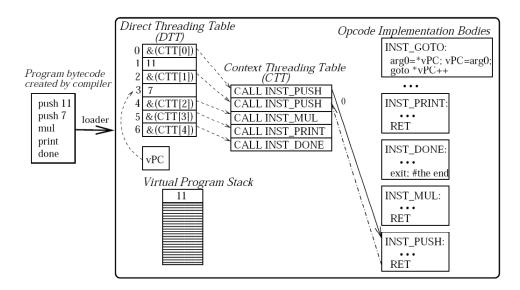

| 3.13 | Stack caching                                                                                   | 36 |

|------|-------------------------------------------------------------------------------------------------|----|

| 3.14 | Lua 5.0 instruction format                                                                      | 39 |

| 3.15 | Branch target buffer organization                                                               | 42 |

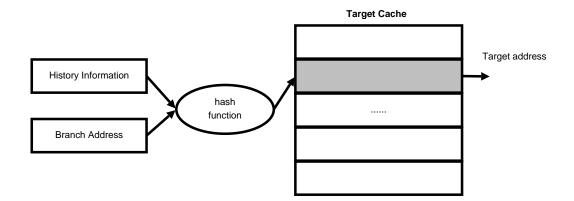

| 3.16 | Structure of a Tagless Target Cache                                                             | 44 |

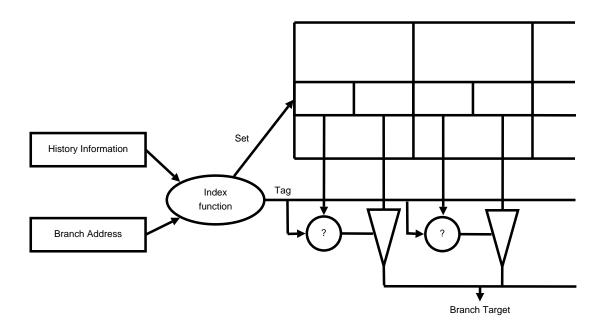

| 3.17 | Structure of a Tagged Target Cache                                                              | 45 |

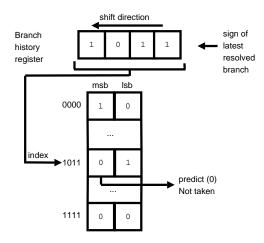

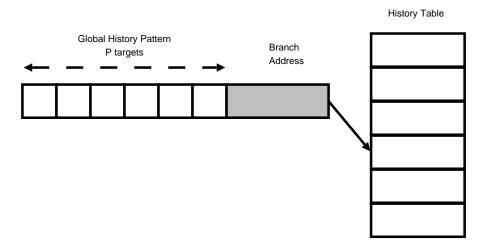

| 3.18 | Two level indirect branch prediction                                                            | 46 |

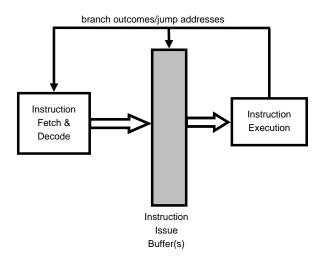

| 3.19 | Instruction fetch and execute mechanisms                                                        | 46 |

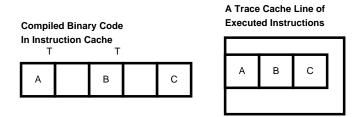

| 3.20 | Non-contiguous compiled code in a contiguous trace cache line $\ldots$ .                        | 47 |

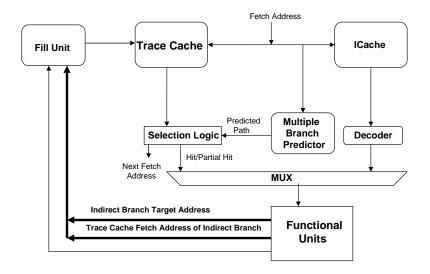

| 3.21 | Trace cache microarchitecture                                                                   | 48 |

| 4.1  | A trace cache line of 3 basic blocks                                                            | 54 |

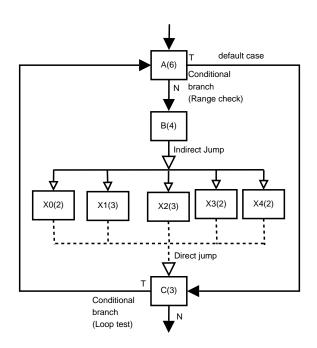

| 4.2  | Sample loop for case study                                                                      | 56 |

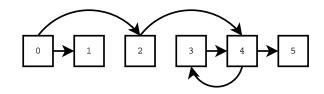

| 4.3  | Basic Block Program Flow Diagram                                                                | 57 |

| 4.4  | Trace cache line layout for the case study example                                              | 57 |

| 4.5  | Cache lines in a set-associative trace cache $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 58 |

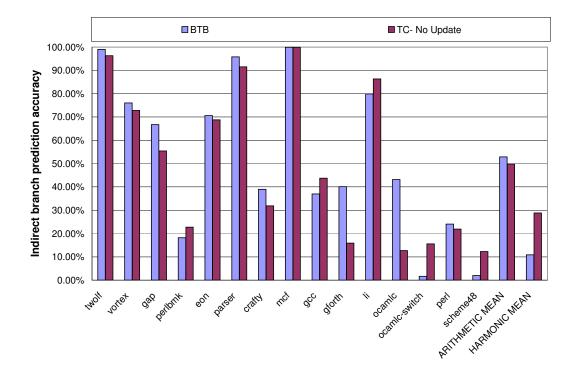

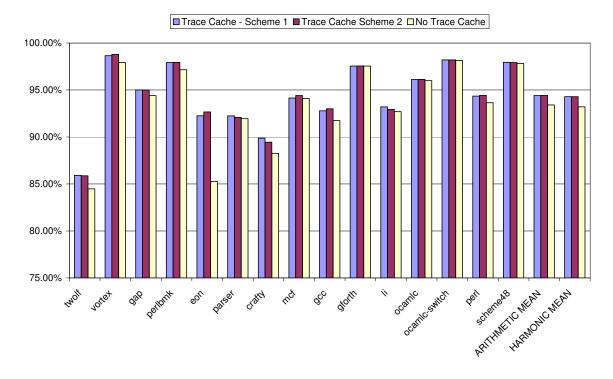

| 4.6  | BTB and TC-No Update pred. rates                                                                | 62 |

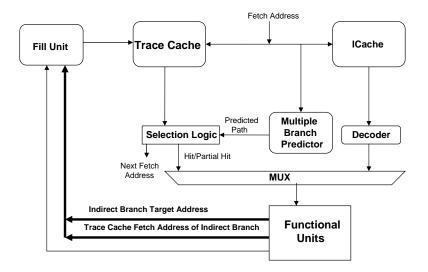

| 4.7  | Trace cache model with the update policy                                                        | 64 |

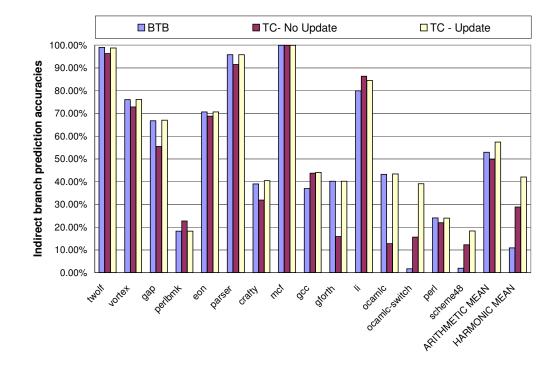

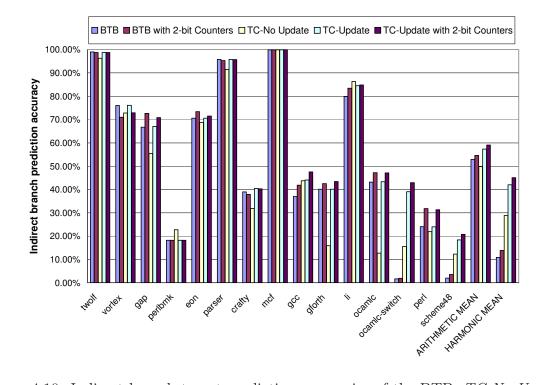

| 4.8  | BTB and TC-No Update and TC-Update pred. rates                                                  | 65 |

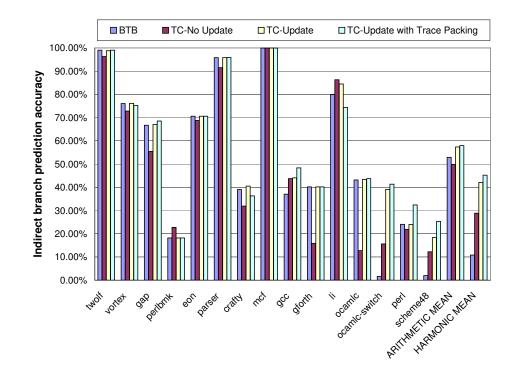

| 4.9  | Pred. rates of BTB and <i>TC-Update</i> with trace packing                                      | 67 |

| 4.10 | Pred. rates of BTB, TC-No Update, TC-Update and TC-Update with                                  |    |

|      | 2-bcs                                                                                           | 69 |

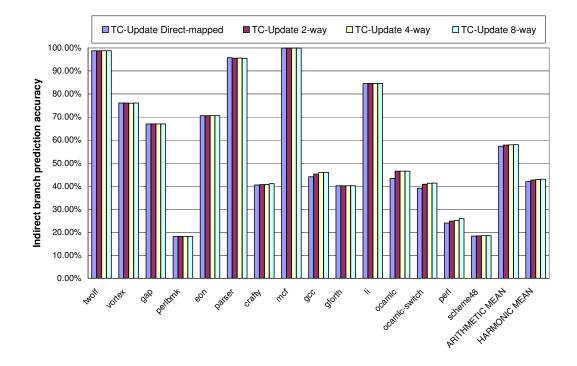

| 4.11 | Pred. rates of the $TC$ - $Update$ model with varying set associativity                         | 70 |

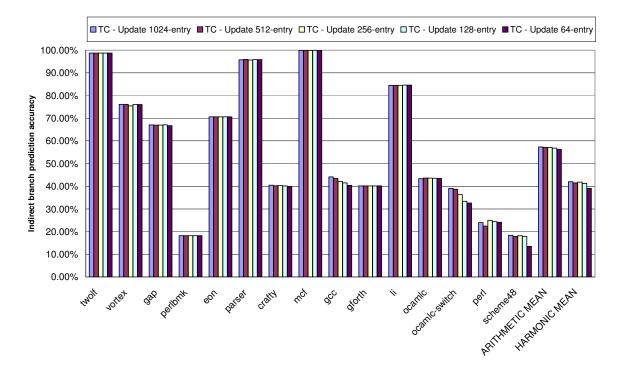

| 4.12 | Pred. rates of the $\mathit{TC-Update}$ model with trace cache size variances                   | 71 |

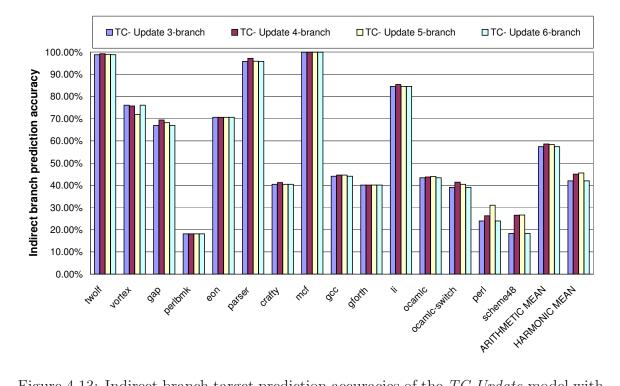

| 4.13 | Pred. rates of the $TC$ - $Update$ model with cache line size variances                         | 73 |

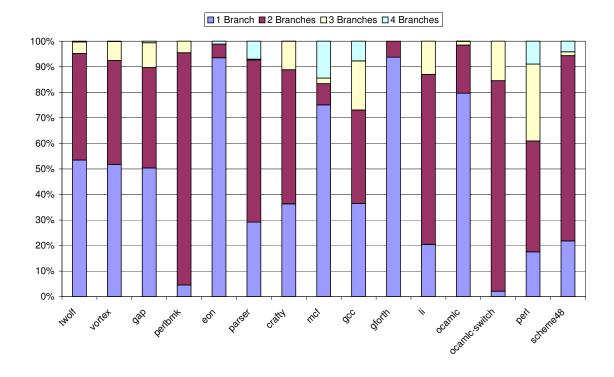

| 4.14 | Distribution of indirect branch trace cache line                                                | 74 |

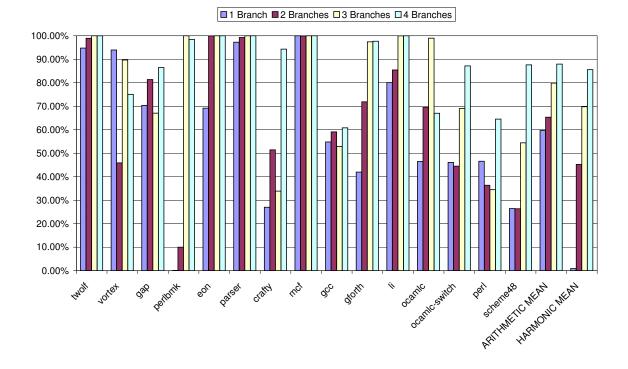

| 4.15 | Pred. rates according to the $\#$ of branches in a trace cache line $\ .$                       | 75 |

| 4.16 | Indirect branch target prediction accuracy of the combined model $\ldots$                       | 76 |

| 4.17 | Trace cache hit rates for different configurations                                              | 77 |

| 4.18 | The percentage of executed instructions from the trace cache                                    | 78 |

| 4.19 | Bimodal direction predication rates with/without a trace cache                                  | 81 |

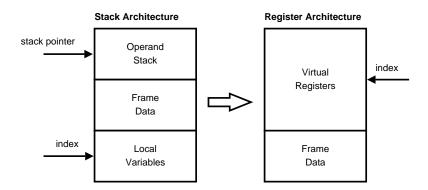

| 5.1  | The structure of a Java frame                                                                   | 92 |

| 5.2  | Stack bytecode to register bytecode translation                                                 | 93 |

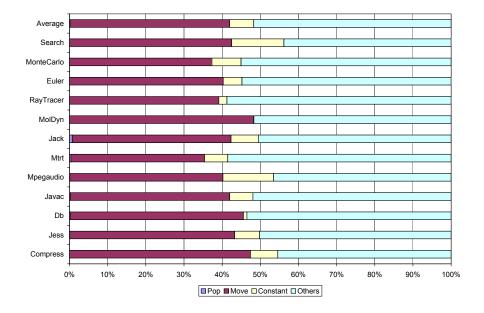

| 5.3  | Different categories of dynamically executed instructions without opt                           | 96 |

| 5.4  | The control flow of the example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 97  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.5  | Source code for the hashCode() method in the java.lang.String                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98  |

| 5.6  | Original stack VM code and corresponding register VM code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 99  |

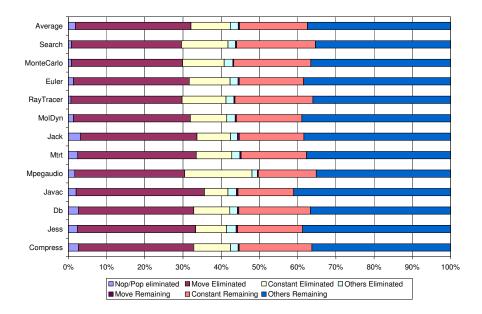

| 6.1  | Breakdown of statically appearing VM instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 103 |

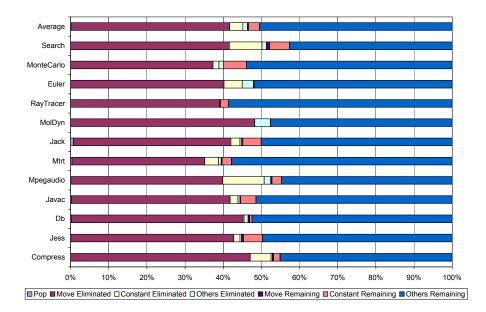

| 6.2  | Breakdown of dynamically appearing VM instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 105 |

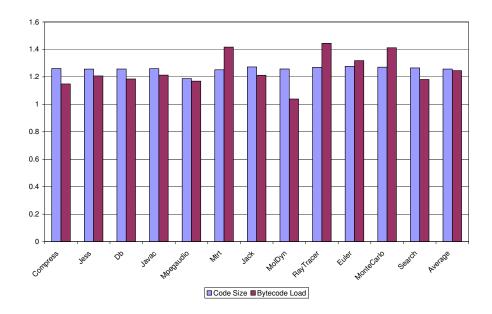

| 6.3  | Code size and by<br>tecode loads $\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfi$ | 106 |

| 6.4  | Ratios of increase in bytecode loads to $\#$ of dispatches eliminated $\ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 107 |

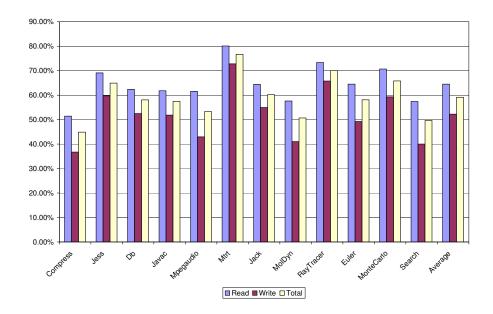

| 6.5  | Stack frame accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 108 |

| 6.6  | Ratios of stack frame accesses to $\#$ of eliminated dispatches $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 109 |

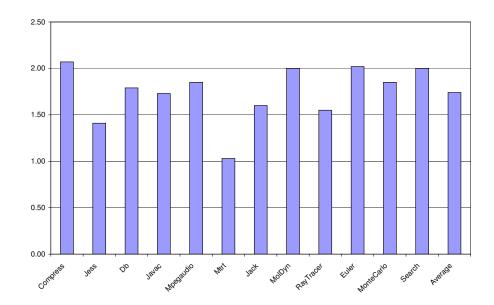

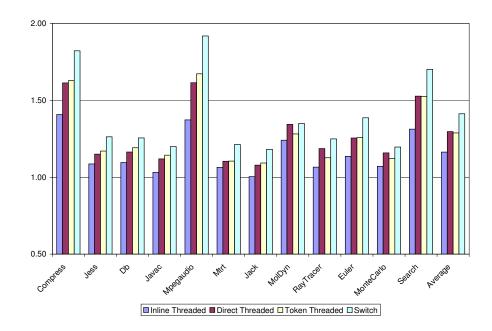

| 6.7  | AMD64 timing results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 111 |

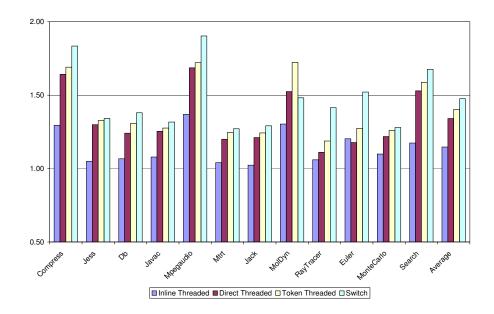

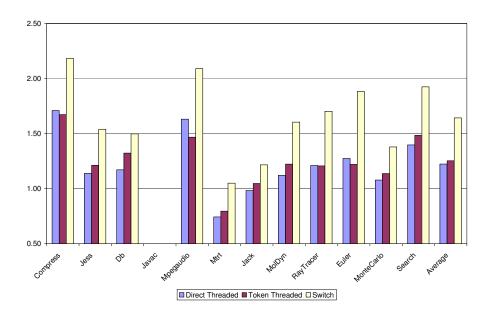

| 6.8  | Intel Pentium 4 timing results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 112 |

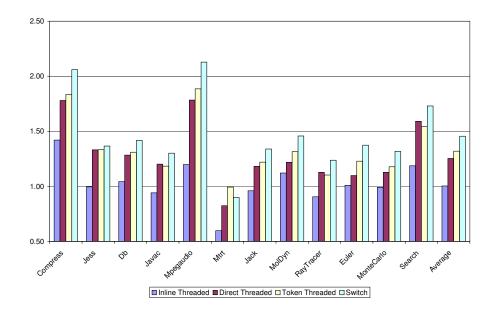

| 6.9  | Intel Core 2 Duo timing results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 112 |

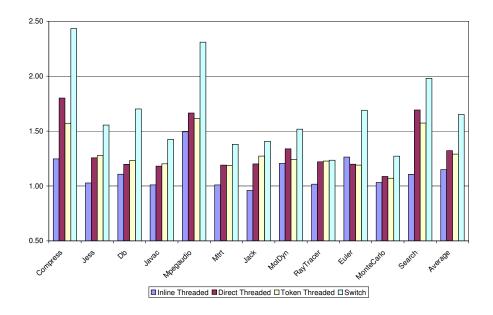

| 6.10 | IBM PowerPC timing results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 113 |

| 6.11 | Alpha timing results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 113 |

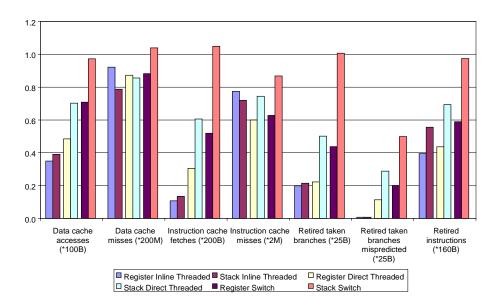

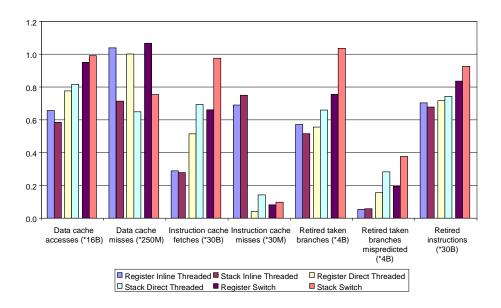

| 6.12 | Compress: AMD64 performance counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 115 |

| 6.13 | Jack: AMD64 performance counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 115 |

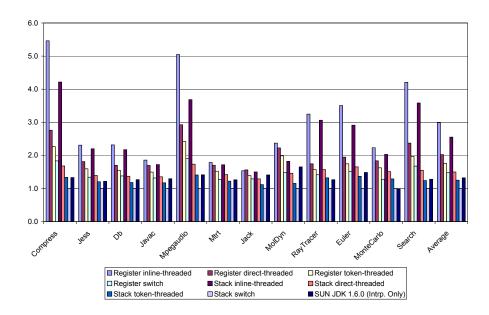

| 6.14 | AMD64: speedups against the stack switch interpreter $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 117 |

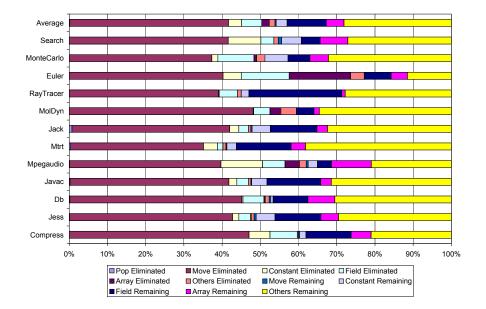

| 6.15 | Breakdown of dynamically appearing VM instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 119 |

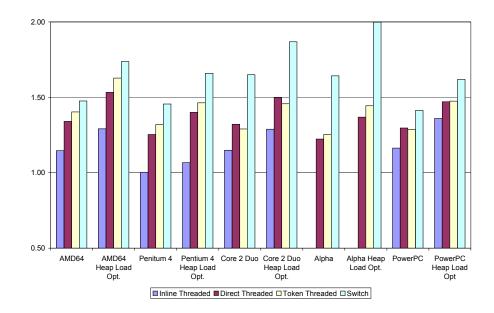

| 6.16 | AMD64 timing results with additional redundant heap load elimination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 120 |

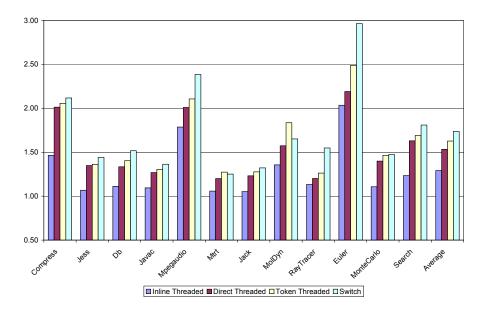

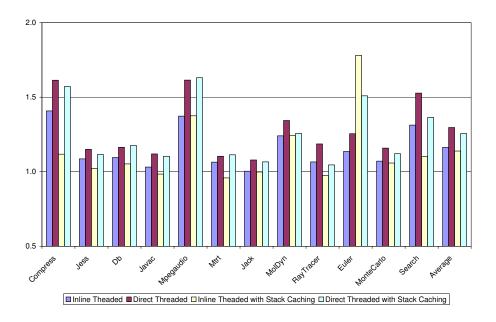

| 6.17 | The same dispatch comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 121 |

| 6.18 | PowerPC timing results with stack caching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 121 |

## Chapter 1

## Introduction

### 1.1 Motivation

Virtual machines (VMs) enable the distribution of programs in an architecture-neutral format, which can easily be interpreted or compiled. The most popular VMs, such as the Java virtual machine (JVM) and Microsoft .NET's common language runtime (CLR), use a virtual stack architecture rather than the register architecture that dominates in real processors.

Interpreters are frequently used to implement virtual machines because they have several practical advantages over native code compilers. Interpreters are much slower than the native code produced by just-in-time compilers (even the fastest interpreters are currently about 5–10 times slower), but they are nonetheless widely used for lightweight language implementations. If written in a high-level language, interpreters are portable; they can simply be recompiled for a new architecture, whereas a just-intime (JIT) compiler requires considerable porting effort. Interpreters also require little memory: the interpreter itself is typically much smaller than a JIT compiler [RVJS00], and the interpreted bytecode is usually a fraction of the size of the corresponding executable native code. For this reason, interpreters are commonly found in embedded systems. Furthermore, interpreters avoid the compilation overhead in JIT compilers. For rarely executed code, interpreting may be much faster than JIT compilation. The Hotspot JVMs [SM01] take advantage of this by using a hybrid interpreter/JIT system. Code is initially interpreted, saving the time and space of JIT compilation, and only if a section of code is executed frequently is it JIT compiled. Interpreters are also dramatically simpler than compilers; they are easy to construct, and easy to debug. Finally, it is easy to provide tools such as debuggers and profilers when using an interpreter because it is easy to insert additional code into an interpreter loop. Providing such tools for native code is much more complex. Interpreters provide a range of attractive features for language implementation. In particular, most scripting languages are implemented using interpreters.

A long-running question in the design of VMs is whether a stack architecture or a register architecture can be implemented more efficiently with an interpreter. Stack architectures allow smaller VM code so less code must be fetched per VM instruction executed. However, stack machines require more VM instructions for a given computation, each of which requires an expensive (usually unpredictable) indirect branch for VM instruction dispatch. Several authors have discussed the issue [Mye77, SM77, MB99, WP97] and presented small examples where each architecture performs better, but no general conclusions can be drawn without a larger study.

#### 1.2 Our Thesis

The main thesis of this work is that register architectures can be implemented to be significantly faster than stack architectures when building a virtual machine interpreter. The main reason is that stack architectures need to shuffle values onto the stack before they can be operated upon, and results must be stored from the stack to variables. In contrast, a register architecture allows VM instructions to manipulate local variables directly. This allows the same functionality to be implemented on a register architecture using far fewer VM instructions. Given that dispatching VM instructions is expensive due to the high cost of real-machine indirect branches, the result is that interpreterbased VMs for register architectures are significantly faster.

### **1.3** Contributions

This dissertation extends previous work on comparing register and stack machine and we believe, answers the question of the relative strengths and weaknesses of stack and register machines. We have made a number of contributions.

• Better analysis of the features of register and stack code

In previous work by Davis et al. [DBC<sup>+</sup>03, GBC<sup>+</sup>05] register and stack code were compared by translating optimized stack code into register code. Although the results were interesting, the quality of the generated register code was poor, and the benefits of register code were underestimated. We use a much more sophisticated scheme to generate our register code (although we also follow the route of translation from optimized stack code) and the result is that our register code requires far fewer VM instructions to implement the same benchmark programs than either corresponding stack code, or register code generated using Davis et al.'s method.

• Design, implementation and measurement of the register VM

Previous work made quantitative measures of the stack and register code, but it did not compare corresponding stack and register VM implementations. This dissertation presents the design and implementation of a register machine that corresponds closely to the stack-based Java VM. We present extensive measurements of both machines, using various interpreter optimization options, and running on several different hardware architectures. Our results include measurements from hardware performance counters that allow us to investigate the effect of using a register rather than stack VM on the microarchitectural behaviour of the interpreter.

• Analysis of the effect of the trace cache on indirect branch prediction

In addition to the core work on virtual machine design, this dissertation also addresses the closely related problem of indirect branch prediction. Indirect branch prediction has a big impact on VM interpreters because interpreters typically use indirect branches to dispatch the execution of VM instructions. A particularly interesting interaction arises with the trace cache which was designed to increase the fetch bandwidth for a superscalar processor. One unintended effect of the trace cache is that it can provide extra context information, which helps indirect branch prediction, particularly when executing programs with a lot of indirect branches, such as interpreters.

### 1.4 Collaborations

During my PhD study, I collaborated with several colleagues. The papers published during my PhD research illustrate our collaborations.

• Yunhe Shi, Emre Özer, and David Gregg. Analyzing effects of trace cache configurations on the prediction of indirect branches. The Journal of Instruction-Level Parallelism, Volume 8, 2006.

Emre Ozer assisted with the research in the trace cache. He provided his expertise in processor microarchitectures and helped to give direction to the experiments. He also contributed considerably to organizing and correcting English in the paper.

• Yunhe Shi, David Gregg, Andrew Beatty, and M. Anton Ertl. Virtual machine showdown: stack versus registers. In ACM/SIGPLAN Conference on Virtual Execution Environments, pages 153-163, Chicago, Illinois, June 2005. ACM Press.

The work in this paper presented our initial results comparing register and stack VMs. The implementation for this paper was based on "CVM", an implementation of the JVM from Sun Microsystems.